| CATALOG PRODUCT DESCRIPTION | ON |

|-----------------------------|----|

|                             |    |

|                             |    |

|                             |    |

|                             |    |

|                             |    |

|                             |    |

|                             |    |

|                             |    |

|                             |    |

|                             |    |

|                             |    |

|                             |    |

|                             |    |

|                             |    |

|                             |    |

|                             |    |

| CATALOG<br>PRODUCT<br>DESCRIPTIONS    |

|---------------------------------------|

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

| · · · · · · · · · · · · · · · · · · · |

|                                       |

|                                       |

| <del></del>                           |

|                                       |

|                                       |

February 1987

# **CONTENTS**

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PAGE<br>NUMBER                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                        |

| SECTION 2 APPLICATION SPECIFIC LOGIC PRODUCTS DIVISION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                        |

| General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                        |

| SECTION 3 PROCESSOR AND COPROCESSOR PRODUCTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                        |

| VL65NC02 CMOS 8-Bit Microprocessor  VL65C816 • VL65C802 CMOS 16-Bit Microprocessor Family  VL82C389 Multibus II Message-Passing Coprocessor  VL86C010 32-Bit RISC Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3–4<br>3–5                                                                                             |

| SECTION 4 PERIPHERAL PRODUCTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                        |

| VL16160 Raster Op ALU  VL1772-02 Floppy Disk Controller/Formatter  VL2793 • VL2797 Floppy Disk Formatter/Controller Family  VL4500A Dynamic RAM Controller  VL4502 Dynamic RAM Controller  VL6522 • VL65C22 Parallel Interface/Timer  VL6765 Double-Density Floppy Disk Controller  VL6845R/E • VL68C45R/S CRT Controller Family and VMC68C45 Megacell Design Kit  VL82C284 CMOS Clock Generator and Interface  VL82C288 CMOS Bus Controller  VL82C37A CMOS Direct Memory Access (DMA) Controller  VL82C54 Programmable Interval Timer  VL82C59A Programmable Intervupt Controller  VL82C84A Clock Generator and Driver  VL82C88 CMOS Bus Controller  VL82C88 CMOS Bus Controller  VL82C88 CMOS Bus Controller  VL82C88 CMOS Clock Generator and Controller  VL85C81 CMOS Clock Generator and Controller | 4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10<br>4-11<br>4-12<br>4-13<br>4-14<br>4-15<br>4-16<br>4-17 |

| VL2010 16 × 16 Parallel Multiplier-Accumulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                        |

| SECTION 6 DATA COMMUNICATIONS PRODUCTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                        |

| VL16C450 • VL82C50A • VL82C50 Asynchronous Communications Element  VL16C452 Dual Asynchronous Communications Element  VL1935 Synchronous Data Line Controller.  VL2123 Dual Enhanced Universal Communications Element (DEUCE)  VL2661 Enhanced Programmable Communications Interface  VL8530 Serial Communications Controller (SCC)  VL85C35 Enhanced Serial Communications Controller (ESCC)                                                                                                                                                                                                                                                                                                                                                                                                            | 6–4<br>6–5<br>6–6<br>6–7<br>6–8                                                                        |

| SECTION 7 TELECOM PRODUCTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                        |

| VL7C103 300 BPS Modem VL7C211 212A/V.22 Modem Filter VL7C212A 300/1200 Bit-per-Second Modem VL7C213 Parallel Bus Modem Controller VL7C214 Stand-Alone Modem Interface Controller VL80C75 T1 Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7–4<br>7–5<br>7–6<br>7–7                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . •                                                                                                    |

## **CONTENTS**

| SECTION 8 APPLICATION SPECIFIC MEMORY PRODUCTS DIVISION  |      |

|----------------------------------------------------------|------|

| General                                                  | 8-3  |

| Line Card                                                | 8–4  |

| Certified EPROM Programmers                              | 8–6  |

| SECTION 9 RAM PRODUCTS                                   |      |

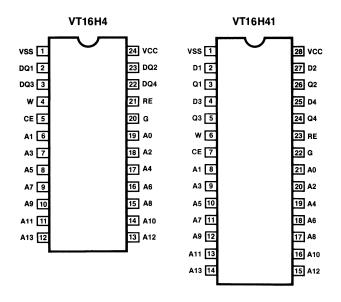

| VT16H4 ● VT16H41 16,384 × 4 HRAM                         | 9–3  |

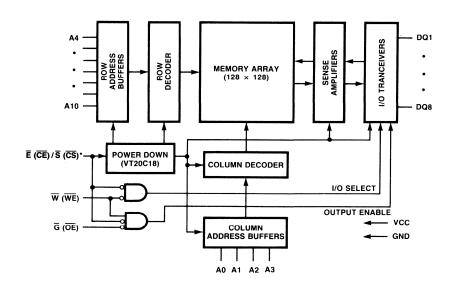

| VT20C18 • VT20C19 2,048 × 8 SRAM                         | 9–4  |

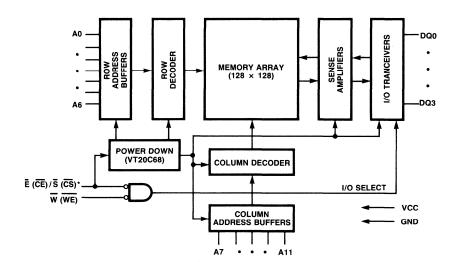

| VT20C68 • VT20C69 4,096 × 4 SRAM                         |      |

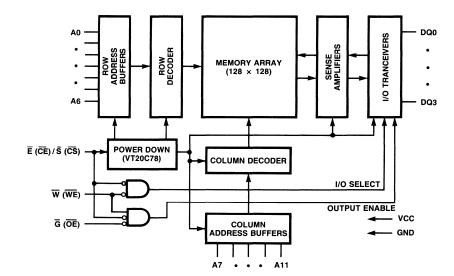

| VT20C78 • VT20C79 4,096 × 4 SRAM                         |      |

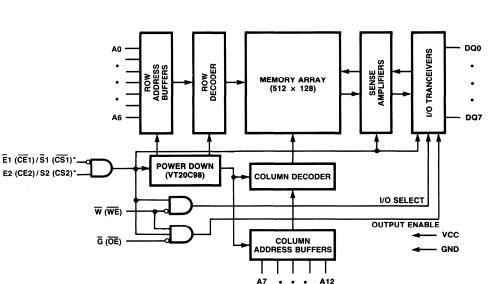

| VT20C98 • VT20C99 8,192 × 8 SRAM                         |      |

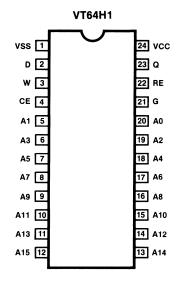

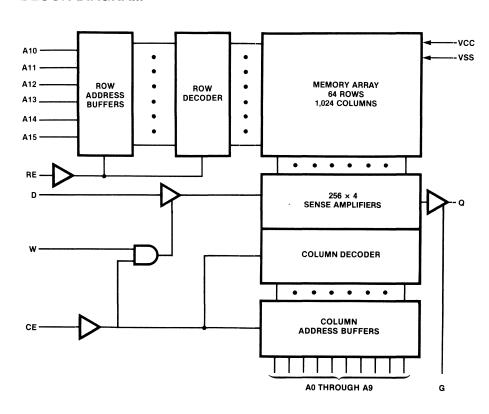

| VT64H1 65,536 × 1 HRAM                                   | 9–8  |

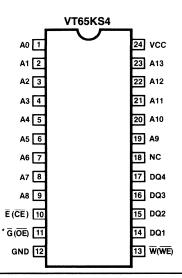

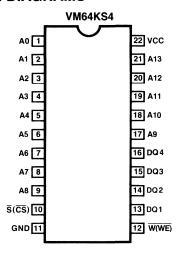

| VT64KS4 ● VT65KS4 16,384 × 4 High-Speed 64K Static RAM   |      |

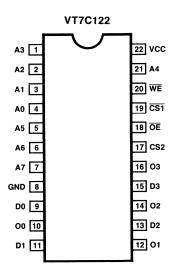

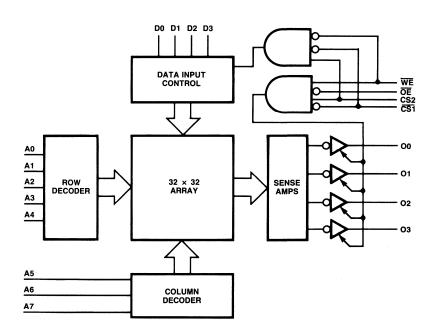

| VT7C122 256 × 4 Static RAM                               | 9–10 |

| SECTION 10 ASM PRODUCTS                                  |      |

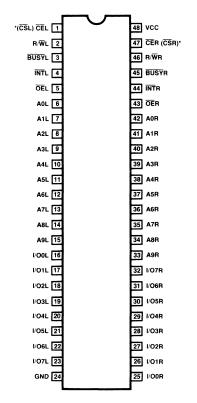

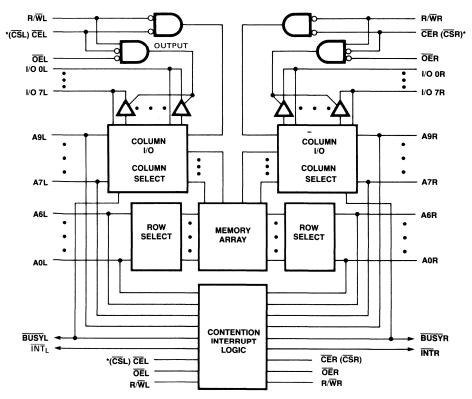

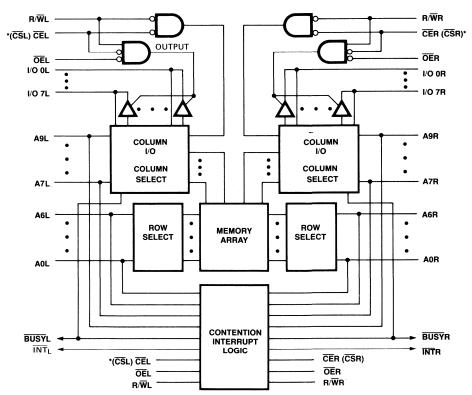

| VT16AM8 1K × 16, 2K × 8 Dual-Port RAM                    |      |

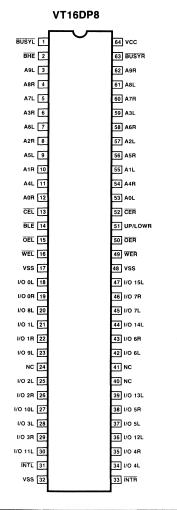

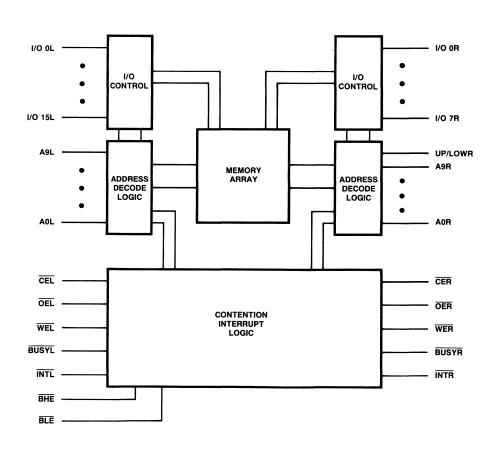

| VT16DP8 1K × 16, 2K × 8 Dual-Port RAM                    |      |

| VT2130 • VT2131 1,024 × 8 Dual-Port Random Access Memory |      |

| VT7132 • VT7142 2K × 8 CMOS Dual-Port RAM                |      |

| VT7132A ● VT7142A High-Speed 2K × 8 CMOS Dual-Port RAM   | 10–7 |

| VT8K9 8,192 × 9 RAM                                      | 10–8 |

| SECTION 11 EPROM PRODUCTS                                |      |

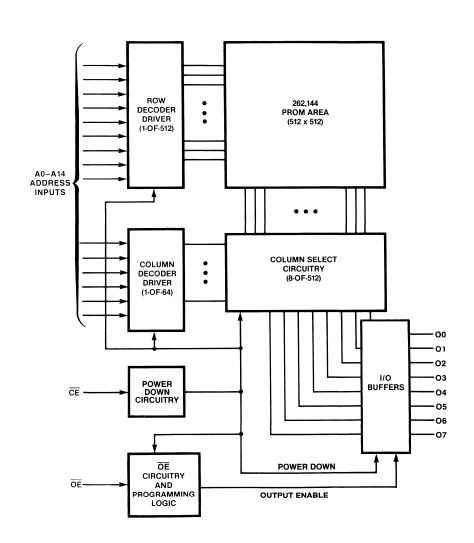

| VT27C128 16,384 × 8 Static CMOS EPROM                    |      |

| VT27C256 32,768 × 8 Static CMOS EPROM                    |      |

| VT27C512 65,536 × 8 Static CMOS EPROM                    |      |

| VT27C64 8,192 × 8 Static CMOS EPROM                      | 11–6 |

| SECTION 12 ROM PRODUCTS                                  |      |

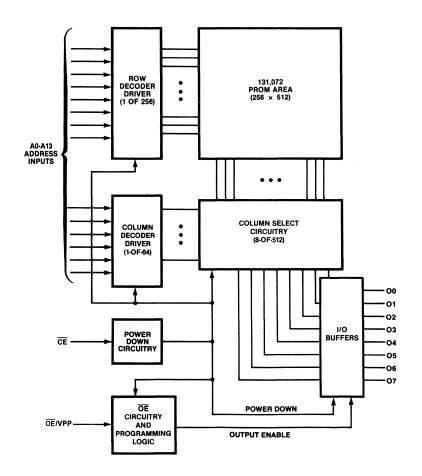

| VT231024 131,070 x 8 Static Read Only Memory             | 12-3 |

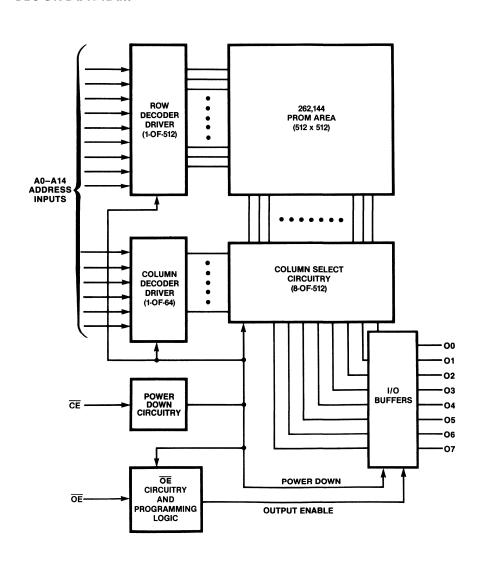

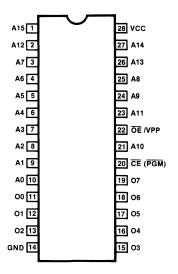

| VT23512 65,536 × 8 Static Read Only Memory               | 12–4 |

| SECTION 13 GOVERNMENT PRODUCTS                           |      |

| General                                                  |      |

| Cross-Reference Guide                                    |      |

| VM2130 • VM2131 1,024 x 8 Dual-Port Random Access Memory | 13–4 |

| VM27C256 32,768 × 8 Static CMOS EPROM                    | 13–5 |

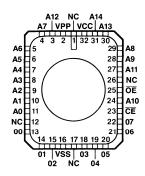

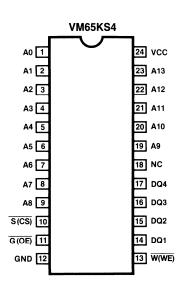

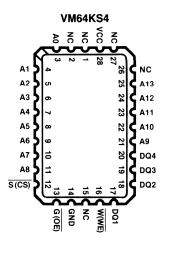

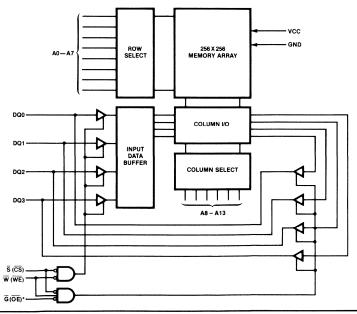

| VM64KS4 • VM65KS4 16,384 × 4 High-Speed 64K Static RAM   | 13–6 |

| SECTION 14 PROGRAMMABLE LOGIC PRODUCTS                   |      |

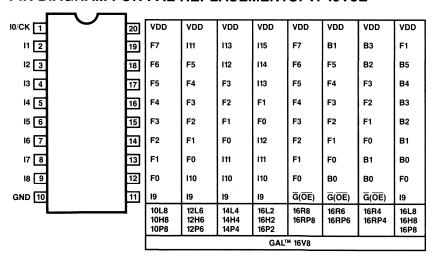

| GAL Cross-Reference Guide                                | 14–3 |

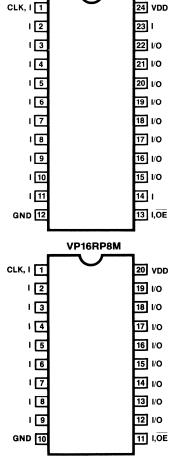

| VP16RP8M ● VP20RP8M CMOS Mask Programmable Logic Array   | 14–4 |

| VP16V8E • VP20V8E Generic Array Logic                    | 14–5 |

| , ,                                                      |      |

SECTION 15 SALES OFFICES, DESIGN CENTERS, AND DISTRIBUTORS

# **NUMERICAL INDEX**

| DEVICE<br>NUMBER                                                                                                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                    | PAGE<br>NUMBER                                                    |

|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| VL16160<br>VL16C450<br>VL16C452                                                                                   | Raster Op ALU                                                                                                                                                                                                                                                                                                                  | 6–3                                                               |

| VL1772-02                                                                                                         | Floppy Disk Controller/Formatter                                                                                                                                                                                                                                                                                               | 4-4                                                               |

| VL1935                                                                                                            | Synchronous Data Line Controller                                                                                                                                                                                                                                                                                               | 6–5                                                               |

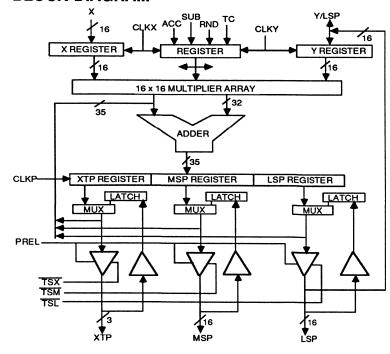

| VL2010<br>VL2044                                                                                                  | 16 × 16 Parallel Multiplier-Accumulator with Preload                                                                                                                                                                                                                                                                           |                                                                   |

| VL2123                                                                                                            | Dual Enhanced Universal Communications Element (DEUCE)                                                                                                                                                                                                                                                                         | 6–6                                                               |

| VL2661                                                                                                            | Enhanced Programmable Communications Interface                                                                                                                                                                                                                                                                                 | 6–7                                                               |

| VL2793<br>VL2797                                                                                                  | Single-Sided Floppy Disk Formatter/Controller                                                                                                                                                                                                                                                                                  |                                                                   |

| VL4500A<br>VL4502                                                                                                 | 8K/16K/32K/64K Dynamic RAM Controller                                                                                                                                                                                                                                                                                          |                                                                   |

| VL65NC02<br>VL6522<br>VL65C22<br>VL65C802<br>VL65C816                                                             | CMOS 8-Bit Microprocessor Parallel Interface/Timer CMOS Parallel Interface/Timer CMOS 16-Bit Microprocessor CMOS 16-Bit Microprocessor                                                                                                                                                                                         | 4–8<br>4–8<br>3–4                                                 |

| VL6765                                                                                                            | Double-Density Floppy Disk Controller                                                                                                                                                                                                                                                                                          | 4–9                                                               |

| VL6845R/E<br>VL68C45R/S                                                                                           | CRT Controller                                                                                                                                                                                                                                                                                                                 |                                                                   |

| VL7C103<br>VL7C211<br>VL7C212A<br>VL7C213<br>VL7C214                                                              | 300 Bit-per-Second Modem                                                                                                                                                                                                                                                                                                       | 7–4<br>7–5<br>7–6                                                 |

| VL80C75                                                                                                           | T1 Interface                                                                                                                                                                                                                                                                                                                   | 7–8                                                               |

| VL82C284<br>VL82C288<br>VL82C37A<br>VL82C389<br>VL82C50<br>VL82C50A<br>VL82C54<br>VL82C59A<br>VL82C84A<br>VL82C88 | CMOS Clock Generator and Interface CMOS Bus Controller CMOS Direct Memory Access (DMA) Controller Multibus II Message-Passing Coprocessor Asynchronous Communications Element Asynchronous Communications Element Programmable Interval Timer Programmable Interrupt Controller Clock Generator and Driver CMOS Bus Controller | 4-12<br>4-13<br>3-5<br>6-3<br>6-3<br>4-14<br>4-15<br>4-16<br>4-17 |

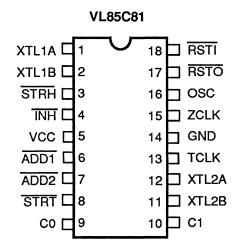

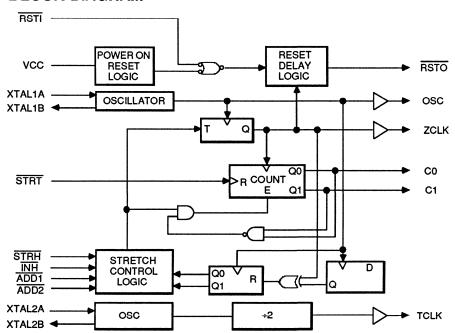

| VL8530<br>VL85C35<br>VL85C81                                                                                      | Serial Communications Controller (SCC) Enhanced Serial Communications Controller (ESCC) CMOS Clock Generator and Controller                                                                                                                                                                                                    | 6–9                                                               |

| VI 86C010                                                                                                         | 32-Bit BISC Microprocessor                                                                                                                                                                                                                                                                                                     | 3_6                                                               |

# **NUMERICAL INDEX**

| DEVICE<br>NUMBER                                                                     | DESCRIPTION                                                                                                                                                                  | PAGE<br>NUMBEI                         |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| VM2130<br>VM2131                                                                     | 1,024 × 8 Dual-Port RAM                                                                                                                                                      | . 13–4<br>. 13–4                       |

| VM27C256                                                                             | 32,768 × 8 Static CMOS EPROM                                                                                                                                                 | 13–5                                   |

| VM64KS4                                                                              | 16,384 × 4 High-Speed 64K Static RAM                                                                                                                                         | 13–6                                   |

| VM65KS4                                                                              | 16,384 × 4 High-Speed 64K Static RAM                                                                                                                                         | 13–6                                   |

| VP16RP8M<br>VP16V8E                                                                  | CMOS Mask Programmable Logic Array                                                                                                                                           | . 14–4<br>. 14–5                       |

| VP20RP8M<br>VP20V8E                                                                  | CMOS Mask Programmable Logic Array                                                                                                                                           |                                        |

| VT16AM8<br>VT16DP8<br>VT16H4<br>VT16H41                                              | Multiplexed 1K × 16, 2K × 8 Dual-Port RAM  1K × 16, 2K × 8 Dual-Port RAM  16,384 × 4 HRAM  16,384 × 4 HRAM                                                                   | 10–4<br>9–3                            |

| VT20C18<br>VT20C19<br>VT20C68<br>VT20C69<br>VT20C78<br>VT20C79<br>VT20C98<br>VT20C99 | 2,048 × 8 SRAM<br>2,048 × 8 SRAM<br>4,096 × 4 SRAM<br>4,096 × 4 SRAM<br>4,096 × 4 SRAM<br>4,096 × 4 SRAM<br>8,192 × 8 SRAM<br>8,192 × 8 SRAM                                 | 9-4<br>9-5<br>9-5<br>9-6<br>9-6<br>9-7 |

| VT2130<br>VT2131                                                                     | 1,024 × 8 Dual-Port RAM                                                                                                                                                      |                                        |

| VT231024<br>VT23512                                                                  | 131,070 × 8 Static ROM                                                                                                                                                       |                                        |

| VT27C128<br>VT27C256<br>VT27C512<br>VT27C64                                          | 16,384 × 8 Static CMOS EPROM 32,768 × 8 Static CMOS EPROM 65,536 × 8 Static CMOS EPROM 8,192 × 8 Static CMOS EPROM                                                           | 11–4<br>11–5                           |

| VT64H1<br>VT64KS4                                                                    | 65,536 × 1 HRAM                                                                                                                                                              |                                        |

| VT65KS4                                                                              | 16,384 × 4 High-Speed SRAM                                                                                                                                                   | 9–9                                    |

| VT7C122<br>VT7132<br>VT7132A<br>VT7142<br>VT7142A                                    | 256 × 4 SRAM 2K × 8 CMOS Dual-Port RAM (Master) High-Speed 2K × 8 CMOS Dual-Port RAM (Master) 2K × 8 CMOS Dual-Port RAM (Slave) High-Speed 2K × 8 CMOS Dual-Port RAM (Slave) | 10–6<br>10–7<br>10–6                   |

| VT8K9                                                                                | 8,192 × 9 RAM                                                                                                                                                                |                                        |

| SECTION 1    |

|--------------|

| INTRODUCTION |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

| ·<br>        |

| <del></del>  |

|              |

|              |

Catalog Product Descriptions

|  | • |  |  |

|--|---|--|--|

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

### INTRODUCTION

#### **GENERAL**

The primary business objective of VLSI Technology, Inc., (VLSI) is to provide systems designers with total application-specific integrated circuit (ASIC) solutions. To accomplish this, it has created a unique blend of expert design tools, leading-edge process technologies, state-of-the-art fabrication facilities, and a wide range of "catalog" devices. An overview of these devices is presented in this short-form catalog. More complete information can be obtained from a VLSI Technology sales office, sales representative, or distributor, or directly from the Divisions.

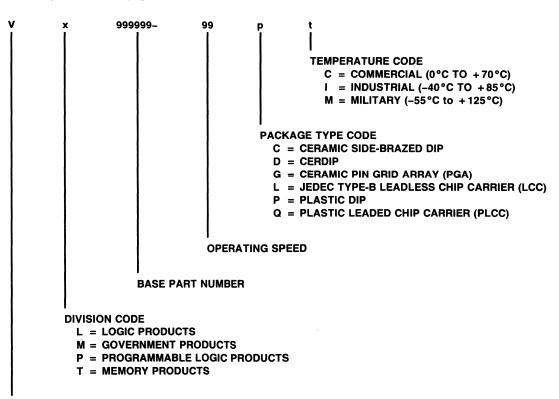

#### ORDERING INFORMATION

VLSI Technology, Inc., products are available in a variety of plastic and ceramic packages, including chip carriers and pin grid arrays, and in different temperature ranges. Specific information on the packages and temperature ranges for a particular device is coded into the part number assigned to it.

For example, the part number VL68C45R-23PC would indicate a CMOS revision R version of the 6845 CRT controller having a 2 MHz bus clock and a 3 MHz character clock, housed in a plastic DIP,

operating over the commercial temperature range, and manufactured by the Logic Products Division. Similarly, the part number VT20C18-20CC would indicate a 2K × 8 16K SRAM having 20 ns access and cycle times, housed in a ceramic side-brazed DIP, operating over the commercial temperature range, and manufactured by the Memory Products Division.

#### PART NUMBER ORGANIZATION

VLSI TECHNOLOGY, INC., IDENTIFIER

| SECTION 2                           |

|-------------------------------------|

| APPLICATION SPECIFIC LOGIC PRODUCTS |

| DIVISION                            |

|                                     |

|                                     |

|                                     |

|                                     |

|                                     |

|                                     |

|                                     |

|                                     |

Catalog Product Descriptions

# APPLICATION SPECIFIC LOGIC PRODUCTS

#### **GENERAL**

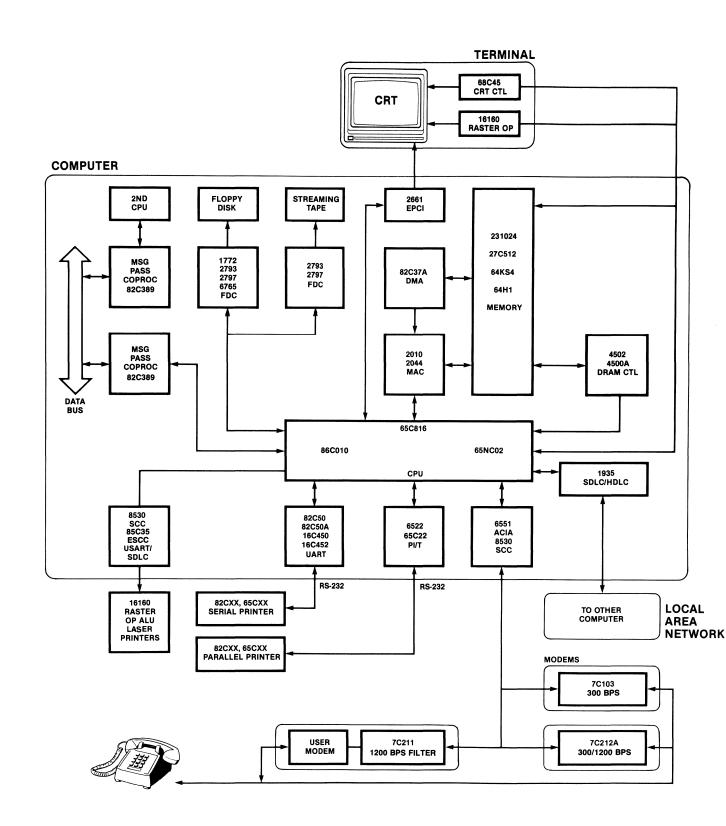

The Application Specific Logic Products Division of VLSI Technology is responsible for the manufacture and marketing of a diverse logic-based product line that encompasses both innovative and proven, well-established catalog devices. This line includes microprocessors and coprocessors, peripheral circuits, digital signal processing devices, and products for data communications and telecommunications applications.

Unlike other suppliers of such devices, however, VLSI is also a recognized leader in ASICs. As such, it not only possesses the design, process, and fabrication capabilities necessary to produce the highest quality off-the-shelf components, but is also able to treat its logic products as an integral part of a complete solution. One of the primary vehicles for accomplishing this is the megacell. The functions represented by individual devices can be implemented as megacells in VLSI's software libraries and used for semicustom circuit design, and functions developed as megacells for specific applications can be turned into catalog products.

The Logic Products Division is located at:

10220 South 51st Street Phoenix, AZ 85044 602/893-8574

# APPLICATION SPECIFIC LOGIC PRODUCTS

#### **TOTAL SYSTEM SOLUTION**

| SECTION 3                          |

|------------------------------------|

| PROCESSOR AND COPROCESSOR PRODUCTS |

| -<br>-                             |

| -<br>-                             |

| <del>-</del><br>-                  |

| -<br>-<br>-                        |

| <del>-</del><br>-                  |

| _<br>_                             |

| -<br>-                             |

| <del></del>                        |

Catalog Product Descriptions

#### **CMOS 8-BIT MICROPROCESSOR**

#### **FEATURES**

- · CMOS silicon-gate technology

- Low power

- -1.1 mA/MHz

- Software-compatible with the NMOS 6502

- Single 5 V power supply required

- · 8-bit parallel processing

- · True indexing capability

- · Programmable stack pointer

- Interrupt capability

- · Non-maskable interrupt

- · 8-bit bidirectional data bus

- Addressable memory range of up to 64K bytes

- · Ready input

- Direct memory access (DMA) capability

- Clock speeds up to 4 MHz

- · Pipelined architecture

- On-chip clock options:

External single-input clock

On-board clock, single external crystal

#### DESCRIPTION

The VL65NC02 is an 8-bit microprocessor device produced using CMOS silicon-gate technology. This device provides advanced system architecture for enhancements in system performance, speed, and value over its NMOS counterparts, the 65XX family of microprocessor devices. The VL65NC02 is the CMOS equivalent of the NMOS 6502, and contains some enhancements. This CMOS type may exhibit different intermediate cycle information from that resident in the NMOS 6502. Intermediate cycle information is not specified, and should not be used.

The VL65NC02 provides 64K bytes of addressable memory and an interrupt input, as well as options for on-chip oscillators and drivers. It is buscompatible and software-compatible with the 65XX CPU family.

#### **CLOCK GENERATOR**

The clock generator develops all internal clock signals and (where applicable) external clock signals associated with the device. It is the clock generator that

drives the timing control unit and the external timing for slave mode operations.

#### TIMING CONTROL

The timing control unit keeps track of the instruction cycle being monitored. The unit is set to zero each time an instruction fetch is executed and is advanced at the beginning of each phase-one clock pulse for as many cycles as are required to complete the instruction. Each data transfer that takes place between the registers depends upon decoding the contents of both the instruction register and the timing control unit.

#### PROGRAM COUNTER

The 16-bit program counter provides the addresses that step the microprocessor through sequential instructions in a program.

Each time the microprocessor fetches an instruction from program memory, the lower byte of the program counter (PCL) is placed on the low-order bits of the address bus and the higher byte of the program counter (PCH) is placed on the high-order 8 bits. The counter is incremented each time an instruction or data is fetched from program memory.

#### **PIN DIAGRAM**

#### VL65NC02 vss RES RDY Ø2 (OUT) 39 23456789 Ø1 (OUT) 38 S.O. 37 Ø0, (IN) N.C. 36 35 34 33 32 31 30 29 28 27 26 25 24 23 N.C. N.C. R/W SYNC VCC D0 D1 A0 D2 A1 10 D3 A2 D4 АЗ 12 A4 D5 13 A5 D6 14 A6 D7 15 A7 A8 A15 16 17 A14 A9 18 A13 A10 19 22 A12 20 VSS

#### **ORDER INFORMATION**

| Part<br>Number | Clock<br>Frequency | Package     |

|----------------|--------------------|-------------|

| VL65NC02-01PC  | 1 MHz              | Plastic DIP |

| VL65NC02-01CC  | I MITIZ            | Ceramic DIP |

| VL65NC02-02PC  | 0.1411             | Plastic DIP |

| VL65NC02-02CC  | 2 MHz              | Ceramic DIP |

| VL65NC02-03PC  | 0.141              | Plastic DIP |

| VL65NC02-03CC  | 3 MHz              | Ceramic DIP |

| VL65NC02-04PC  | 4 1 41 1-          | Plastic DIP |

| VL65NC02-04CC  | 4 MHz              | Ceramic DIP |

# VL65C816•VL65C802

## **CMOS 16-BIT MICROPROCESSOR FAMILY**

#### **FEATURES**

- Advanced CMOS design for low power consumption and increased noise immunity

- Single 3 6 V power supply, 5 V specified

- Emulation mode allows complete hardware and software compatibility with 6502 designs

- 24-bit address bus allows access to 16M bytes of memory space

- Full 16-bit ALU, Accumulator, Stack Pointer, and Index Registers

- Valid data address (VDA) and valid program address (VPA) output allows dual cache and cycle steal DMA implementation

- Vector pull (VP) output indicates when interrupt vectors are being addressed

- VP may be used to implement vectored interrupt design

- ABORT input and associated vector supports interrupting any instruction without modifying internal registers

- Separate program and data bank registers allow program segmentation

- New Direct Register allows "zero page" addressing anywhere in first 64K bytes

- 24 addressing modes: 13 original 6502 modes plus 11 new addressing modes, with 91 instructions using 255 opcodes

- New Wait for Interrupt (WAI) and Stop the Clock (STP) instructions further reduce power consumption, decrease interrupt latency and allow synchronization with external events

- New Co-Processor (COP) instruction with associated vector supports coprocessor configurations (e.g., floating point processors)

#### DESCRIPTION

The VL65C802 and VL65C816 are CMOS 16-bit microprocessors featuring total software compatibility with their 8-bit NMOS and CMOS 6500-series predecessors. The VL65C802 is pin-forpin compatible with 8-bit devices currently available, while the VL65C816 extends addressing to a full 16 megabytes. These devices offer the many advantages of CMOS technology,

including increased noise immunity, higher reliability, and greatly reduced power requirements. A software switch determines whether the processor is in the 8-bit "emulation" mode or in the "native" mode, thus allowing existing systems to use the expanded features.

The Accumulator, ALU, X and Y Index registers, and Stack Pointer Register have all been extended to 16 bits. A new 16-bit Direct Page Register augments the direct page addressing mode (formerly zero page addressing). Separate Program Bank and Data Bank Registers allow 24-bit memory addressing.

Four new signals provide the system designer with many options. The ABORT input can interrupt the currently executing instruction without modifying internal registers. Valid data address (VDA) and Valid program address (VPA) outputs facilitate dual cache memory by indicating whether a data segment or program segment is accessed. Modifying a vector is made easy by monitoring the vector pull (VP) output.

#### **PIN DIAGRAMS**

#### VL65C816 VL65C802 RES 02 (OUT) 50 02 (IN) 00 NC 00 NC VP d1 RES vss □1 40 40 RDY 🗆 39 □ VDA RDY d 2 39 ABORT 3 **Ы** м/х 38 Ø1 (OUT) 38 TRQ 4 Ø2 (IN) 37 TRQ 37 ML d5 □ BE 36 NC [ 36 5 ЬЕ NMI 35 NMI d 35 6 6 □ R/W $\Box RW$ VPA SYNC d 7 VDD 8 33 DO/BAO VDD 8 33 D D0 A0 🗖 9 A0 🗆 9 32 D1/BA1 32 □ D1 A1 口10 31 A1 口 10 31 ☐ D2/BA2 □ D2 D3 D4 D5 D6 30 30 A2 [ 11 D3/BA3 A2 11 A3 🗆 12 29 D4/BA4 АЗ 12 29 13 28 D5/BA5 Α4 13 28 27 D6/BA6 Α5 14 27 Α5 14 A6 🗖 26 D7 Ь **A6** 15 26 D7/BA7 15 25 A A15 25 ☐ A15 Α7 □16 Α7 16 **d**17 □ A14 **8**A 口17 24 D A14 **A8** 24 **□** A13 □18 23 A A13 □18 23 Α9 Α9 **1**9 22 A12 A10 **1**19 ☐ A12 A10 d 21 🗖 VSS **20** VSS A11 20

#### ORDER INFORMATION

| Part<br>Number                                                   | Clock<br>Frequency | Package                                                  |

|------------------------------------------------------------------|--------------------|----------------------------------------------------------|

| VL65C802-02PC<br>VL65C802-02CC<br>) VL65C816-02PC                | 2 MHz              | Plastic DIP<br>Ceramic DIP<br>Plastic DIP                |

| VL65C816-02CC                                                    |                    | Ceramic DIP                                              |

| VL65C802-04PC<br>VL65C802-04CC<br>VL65C816-04PC<br>VL65C816-04CC | 4 MHz              | Plastic DIP<br>Ceramic DIP<br>Plastic DIP<br>Ceramic DIP |

| VL65C802-06PC<br>VL65C802-06CC<br>VL65C816-06PC<br>VL65C816-06CC | 6 MHz              | Plastic DIP<br>Ceramic DIP<br>Plastic DIP<br>Ceramic DIP |

| VL65C802-08PC<br>VL65C802-08CC<br>VL65C816-08PC<br>VL65C816-08CC | 8 MHz              | Plastic DIP<br>Ceramic DIP<br>Plastic DIP<br>Ceramic DIP |

# MESSAGE-PASSING COPROCESSOR MULTIBUS® II

#### **FEATURES**

- Full-function, single-chip interface to Parallel System Bus ( iPSB )

- Implements full message-passing protocol on iPSB bus

- Offloads managing iPSB bus arbitration, transfer and exception cycles from local CPU

- Compatible with Bus Arbiter/ Controller (BAC) and Message Interrupt Controller (MIC) interface designs

- Maximizes performance on iPSB bus and local on-board bus

- Simplifies highly functional interconnect space implementations for both local and iPSB buses

- Processor-independent interface to iPSB bus

- Supports co-existence of dual-port and message-passing architectures

#### DESCRIPTION

The VL82C389 Message Passing Coprocessor (MPC) provides a high-integration interface solution for the Parallel System Bus ( iPSB ) of the Multibus II architecture. The device integrates the logic necessary to implement a full bus interface solution, including support for message passing and interconnect spaces, as well as memory and I/O references on the iPSB bus. In addition, the MPC is designed to simplify implementation of dual-port memory functions for those designs that must co-exist with message passing.

The message address space in the MULTIBUS II architecture has been defined to provide a high-performance interprocessor communication mechanism for multiprocessor systems. By performing the message space interface, the VL82C389 MPC offloads the interprocessor communication tasks from the local on-board CPU, which decouples the local bus activities from the iPSB bus activities. Decoupling

these two functions eliminates an interface bottleneck present in traditional dual-port architectures. The bottleneck is a result of having a dual-port architecture that requires a tight coupling between a processor and some shared memory resource of limited size. Unfortunately, as the number of processors increases, the dual-port structure degrades system performance even more dramatically.

Using the MPC component to decouple these resources yields several enhancements to system performance. For example, resources on the local processor bus and parallel system bus are not held in wait states while arbitration for other resources is performed. In addition, each transfer can occur at the full bandwidth of the associated bus. The benefit of this is the increased overall system performance that results from processors being able to process other tasks in parallel, with message transfers being handled by the MPC component.

#### **BLOCK DIAGRAM**

#### LOCAL BUS INTERFACE LOCAL BUS MULTIPLEXING BLIFFERS AND CONTROL INTERNAL LOCAL BUS INTERCONNECT REGISTERS AND MEMORY, I/O AND MESSAGE INTERCONNECT **BUFFERS AND** OPERATION REFERENCE CONTROL CONTROL CONTROL INTERCONNECT BUS SPACE INTERFACE DUAL-PORT INTERNAL IPSB BUS MEMORY CONTROL INTERFACE **ARBITRATION** DUAL TRANSFER AND POR1 **EXCEPTION** CONTROL CONTROL **IPSB BUS INTERFACE**

### $^{\circledR}$ Multibus is a registered trademark of Intel Corp.

#### ORDER INFORMATION

| Part<br>Number | Package                            |

|----------------|------------------------------------|

| VL82C389-GC    | Ceramic Pin<br>Grid Array<br>(PGA) |

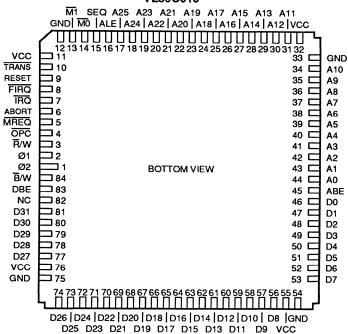

#### 32-BIT RISC MICROPROCESSOR

#### DESCRIPTION

- · 32-bit internal architecture

- 32-bit external data bus

- · 64M-byte linear address space

- Bus timing optimized for standard DRAM usage with page mode operation

- · 32M-byte/second bus bandwidth

- Simple/powerful instruction set providing an excellent high level language compiler target

- Hardware support for virtual memory systems

- Low interrupt latency for real-time application requirements

- Full CMOS implementation results in low power consumption

- Single 5 V ± 5% operation

- 84-pin JEDEC Type-B leadless chip carrier or plastic leaded chip carrier (PLCC)

#### **FEATURES**

The VL86C010 Acorn RISC Machine (ARM) is a full 32-bit general-purpose microprocessor designed using reduced instruction set computer (RISC) methodologies. The processor is targeted for the microcomputer, graphics, industrial and controller markets for use in stand-alone or embedded systems. Applications in which the processor is useful include laser printers, graphics engines, N.C. machines and any other systems requiring fast real-time response to external interrupt sources and high processing throughput.

The VL86C010 features a 32-bit data bus, 25 registers of 32 bits each, a load-store architecture, a partially overlapping register set, 3 µs worst-case interrupt latency, conditional instruction execution, a 26-bit linear address space and an average instruction execution rate of from three-to-four million instructions per second (MIPS). Additionally, the processor supports two addressing modes: program counter (PC) and base register relative modes. The ability to do pre- and post-indexing allows

stacks and queues to be easily implemented in software. All instructions are 32 bits long (aligned on word boundaries), with register-to-register operations executing in one cycle. The two data types supported are 8-bit bytes and 32-bit words.

Using a load-store architecture simplifies the execution unit of the processor, since only a few instructions deal directly with memory and the rest operate register-to-register. Load and store multiple register instructions provide enhanced performance, making context switches faster and exploiting sequential memory access modes.

The processor supports two types of interrupts that differ in priority and register usage. The lowest latency is provided by the fast interrupt request (FIRQ) which is used primarily for I/O to peripheral devices. The other interrupt type (IRQ) is used for interrupt routines that do not demand low-latency service or where the overhead of a full context switch is small compared with the interrupt process execution time.

#### **PIN DIAGRAM**

#### JEDEC TYPE-B CERAMIC LEADLESS CHIP CARRIER

#### VL86C010

#### ORDER INFORMATION

| Part<br>Number | Clock<br>Frequency | Package                               |

|----------------|--------------------|---------------------------------------|

| VL86C010-04QC  | 4 MHz              | Plastic Leaded<br>Chip Carrier (PLCC) |

| VL86C010-04LC  | 4 IVITIZ           | JEDEC Type-B<br>Ceramic Carrier       |

| VL86C010-08QC  | 8 MHz              | Plastic Leaded<br>Chip Carrier (PLCC) |

| VL86C010-08LC  | O IVITIZ           | JEDEC Type-B<br>Ceramic Carrier       |

| SECTION 4  |

|------------|

| PERIPHERAL |

| PRODUCTS   |

|            |

|            |

|            |

|            |

|            |

|            |

|            |

|            |

|            |

|            |

|            |

|            |

Catalog Product Descriptions

#### **RASTER OP ALU**

#### **FEATURES**

- Provides hardware assist for bitmapped graphics operations. Includes 32-bit barrel shifter

- Performance increase over software implementations:

- Monochrome = 4 X Software

- Color = 4 X (Planes) X Software

- Supports both CRT displays and such hardcopy devices as laser printers

- Compatible with both monochrome and color displays

- Implements all 256 possible raster operations on source, destination, and pattern data

- 28-pin package; 5 V supply

#### DESCRIPTION

The VL16160 Raster Op ALU (RALU) provides hardware-assisted performance enhancements for bit manipulation operations used in bit-mapped graphics displays. These operations, commonly called bit block translation (BITBLT), allow bit-mapped images to be combined and manipulated by logical operators. These operators include AND, OR, and XOR, and can be used on source, destination, and pattern data. Additionally, support for masking with multiple mask registers for clipping is included.

The BITBLT operation is general purpose enough to be used in a wide range of graphics operations, including text display using arbitrary fonts,

attributes, and enhancements. Successive applications of BITBLT can perform such operations as scaling, filling, rotations, and texturing.

In a typical application, the RALU operates on display data in 16-bit words that are latched into its input buffers by external hardware. Once source, destination, pattern, shift, and masking data are loaded into the RALU, the source data is bit-aligned with the destination data, and the logical operation specified in the function register takes place. The results are stored in the ALU Output Register, which can be output onto the bus by a single strobe signal.

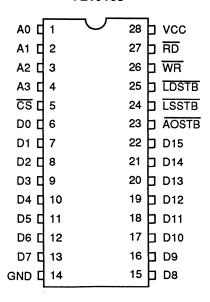

#### **PIN DIAGRAM**

#### VL16160

#### **BLOCK DIAGRAM**

#### ORDER INFORMATION

| Part<br>Number | Package                            |

|----------------|------------------------------------|

| VL16160-PC     | Plastic DIP                        |

| VL16160-CC     | Ceramic DIP                        |

| VL16160-QC     | Plastic Leaded Chip Carrier (PLCC) |

#### FLOPPY DISK CONTROLLER/FORMATTER

#### **FEATURES**

- · Built-in data separator

- · Built-in write precompensation

- Single and double density

- Motor control

- 128, 256, 512, or 1024 sector lengths

- · TTL compatible

- · 8-bit bidirectional data bus

- · Fast step rates

- 28-pin DIP

- Single 5 V power supply

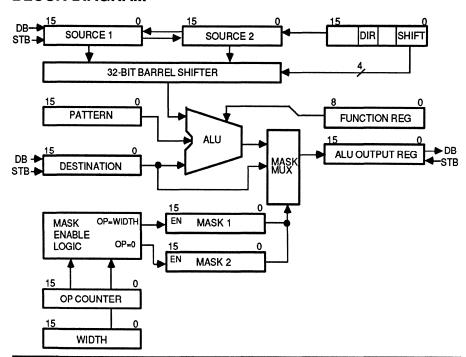

#### **DESCRIPTION**

The VL1772-02 is an MOS/LSI device that performs the functions of a 5 1/4-inch floppy disk controller/formatter. It replaces the older 1770-type device.

The drive side of the interface needs no additional logic except for buffers/ receivers. Designed for 5 1/4-inch single- or double-density operation, the device contains a programmable Motor On signal.

The VL1772-02 is implemented in NMOS silicon-gate technology and is available in a 28-pin dual in-line package. It is a low-cost version of the WD179X Floppy Disk Controller/Formatter and is compatible with generic 179X types. It also has a built-in digital data separator and write precompensation circuits. A single read (RD) line (pin 19) is the only input required to recover serial FM or MFM data from the disk drive. The device has been specifically designed for control of floppy disk drives with data

rates of 125K bps (single density) and 250K bps (double density). In addition, it can write a precompensation that is125 ns from nominal, and can be enabled at any point through simple software commands. Another programmable feature, Motor On, has been incorporated to automatically enable the spindle motor prior to operating a selected drive. The VL1772-02 offers stepping rates of 2, 3, 6, and 12 ms

The processor interface consists of an 8-bit bidirectional bus for transfer of the status information, data, and commands. All host communication with the drive occurs through these data lines. They are capable of driving one standard TTL load or three LS loads.

#### PIN DIAGRAM

#### VL1772-02

#### **BLOCK DIAGRAM**

#### ORDER INFORMATION

| Part<br>Number                            | Package                                                    |

|-------------------------------------------|------------------------------------------------------------|

| VL1772-02PC<br>VL1772-02QC<br>VL1772-02CC | Plastic DIP Plastic Leaded Chip Carrier (PLCC) Ceramic DIP |

### FLOPPY DISK FORMATTER/ CONTROLLER FAMILY

#### **FEATURES**

- ON-CHIP PLL DATA SEPARATOR

- ON-CHIP WRITE PRECOMPENSATION LOGIC

- SINGLE +5V SUPPLY

- ACCOMMODATES SINGLE AND DOUBLE DENSITY FORMATS

IBM 3740 (FM) IBM 34 (MFM)

- AUTOMATIC SEEK WITH VERIFY

- MULTIPLE SECTOR READ/WRITE

- TTL COMPATIBLE

- PROGRAMMABLE CONTROL

SELECTABLE TRACK-TO-TRACK ACCESS

HEAD LOAD TIMING

- SOFTWARE COMPATIBLE WITH THE FD179X SERIES

- SOFT SECTOR FORMAT COMPATIBILITY

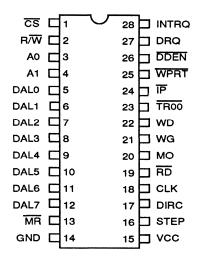

#### **DESCRIPTION**

The VL279X are N-Channel Silicon Gate MOS LSI devices which perform the functions of a Floppy Disk Formatter/Controller in a single chip implementation. The VL279X, which can be considered the end result of both the FD1771 and FD179X designs, is IBM 3740 compatible in single density mode (FM) and System 34 compatible in Double Density Mode (MFM). The VL279X contains all the features of its predecessor the FD179X plus a high performance Phase-Lock-Loop Data Separator as well as Write Precompensation Logic. In Double Density mode, Write Precompensation is automatically engaged to a value programmed via an external potentiometer. In order to maintain compatibility, the FD1771, FD179X and VL279X designs were made as close as possible with the computer interface, instruction set, and I/O registers being identical. Also, head load control is identical. In each case, the actual pin assignments vary by only a few pins from any one to another.

The processor interface consists of an 8-bit bi-directional bus for data, status, and control word transfers. The VL279X is set up to operate on a multiplexed bus with other bus-oriented devices.

The VL279X is TTL compatible on all inputs and outputs. The outputs will drive one TTL load or three LS loads. The 2793 is identical to the 2791 except the DAL lines are TRUE for systems that utilize true data busses.

The 2797 has a side select output for controlling double-sided drives.

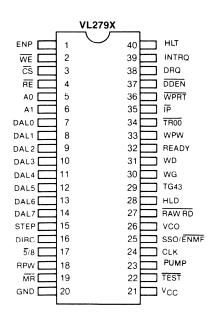

#### PIN DIAGRAM

#### ORDER INFORMATION

| Part<br>Number | Format  | Package     |

|----------------|---------|-------------|

| VL2793-PC      | Single- | Plastic DIP |

| VL2793-CC      | Sided   | Ceramic DIP |

| VL2797-PC      | Double- | Plastic DIP |

| VL2797-CC      | Sided   | Ceramic DIP |

#### Note:

#### DYNAMIC RAM CONTROLLER

#### **FEATURES**

- Controls operation of 8K/16K/32K/64K dynamic RAMs

- Creates static RAM appearance

- One package contains address multiplexer, refresh control and timing control

- Directly addresses and drives up to 256K bytes of memory without external drivers

- Operates from microprocessor clock

- No crystals, delay lines, or RC networks

- Eliminates arbitration delays

- Refresh may be internally or externally initiated

- Ability to synchronize or interleave controller with the microprocessor system (including multiple controllers)

- 3-state outputs allow multiport memory configuration

- Performance ranges of 150 ns/200 ns/250 ns

- Compatible with TI TMS 4500A

#### **DESCRIPTION**

The VL4500A is a monolithic DRAM system controller designed to provide address multiplexing, timing, control and refresh/access arbitration functions to simplify the interface of dynamic RAMs to microprocessor systems.

The controller contains a 16-bit multiplexer that generates the address lines for the memory device from the 16 system address bits and provides the strobe signals required by the memory to decode the address. An 8-bit refresh counter generates the 256-row addresses required to refresh.

A refresh timer is provided that generates the necessary timing to refresh the dynamic memories and assure data retention.

The VL4500A also contains refresh/access arbitration circuitry to resolve conflicts between memory access requests and memory refresh cycles.

#### **PIN DIAGRAM**

#### **VL4500A**

#### **BLOCK DIAGRAM**

#### ORDER INFORMATION

| Part<br>Number               | Access<br>Time | Package                    |

|------------------------------|----------------|----------------------------|

| VL4500A-15PC<br>VL4500A-15CC | 150 ns         | Plastic DIP<br>Ceramic DIP |

| VL4500A-20PC<br>VL4500A-20CC | 200 ns         | Plastic DIP<br>Ceramic DIP |

| VL4500A-25PC<br>VL4500A-25CC | 250 ns         | Plastic DIP<br>Ceramic DIP |

Note:

#### DYNAMIC RAM CONTROLLER

#### **FEATURES**

- Inputs are TTL voltage compatible

- Controls operation of 64K and 256K dynamic RAMs

- Creates static RAM appearance

- One package contains address multiplexer, refresh control and timing control

- Directly addresses and drives up to 2 megabytes of memory without external drivers

- Operates from microprocessor clock

- —No crystals, delay lines, or RC networks

- —Eliminates arbitration delays

- Refresh may be internally or externally initiated

- High performance CMOS technology

- Strap-selected wait state generation for microprocessor/ memory speed matching

- Ability to synchronize or interleave controller with the microprocessor system (including multiple controllers)

- 3-state outputs allow multiport memory configuration

- Performance ranges of 150 ns/200 ns

- Compatible with VLSI VL4500A and TI TMS4500A, THCT4502

#### **DESCRIPTION**

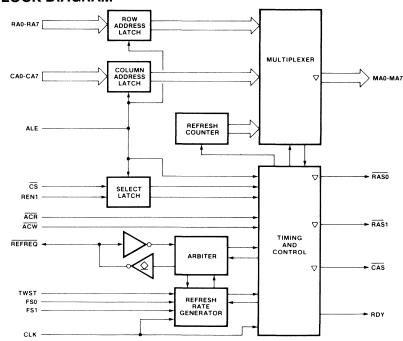

The VL4502 is a monolithic DRAM system controller providing address multiplexing, timing, control and refresh/access arbitration functions to simplify the interface of dynamic RAMs to microprocessor systems.

The controller contains an 18-bit multiplexer that generates the address lines for the memory device from the 18 system address bits and provides the strobe signals required by the memory to decode the address. A 9-bit refresh counter generates up to 512 row addresses required to refresh.

A refresh timer is provided that generates the necessary timing to refresh the dynamic memories and assure data retention.

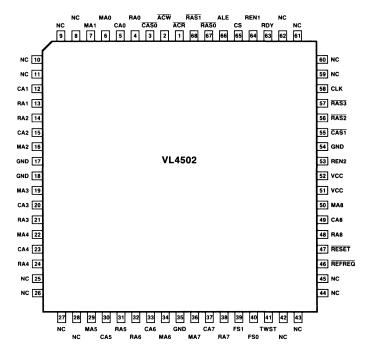

#### **PIN DIAGRAMS**

#### ORDER INFORMATION

| Part<br>Number                            | Access<br>Time | Package                                                    |  |

|-------------------------------------------|----------------|------------------------------------------------------------|--|

| VL4502-15PC<br>VL4502-15CC<br>VL4502-15QC | 150 ns         | Plastic DIP Ceramic DIP Plastic Leaded Chip Carrier (PLCC) |  |

| VL4502-20PC<br>VL4502-20CC<br>VL4502-20QC | 200 ns         | Plastic DIP Ceramic DIP Plastic Leaded Chip Carrier (PLCC) |  |

Note:

#### PARALLEL INTERFACE/TIMER

#### **FEATURES**

- Low-power consuming CMOS parallel interface/timer (VL65C22)

- Low-cost HMOS parallel interface/timer (VL6522)

- Two 8-bit bidirectional I/O ports

- Two 16-bit timer/counters

- Serial bidirectional peripheral I/O

- Enhanced handshake features

- Programmable Data Direction Registers

- TTL compatible I/O peripheral lines

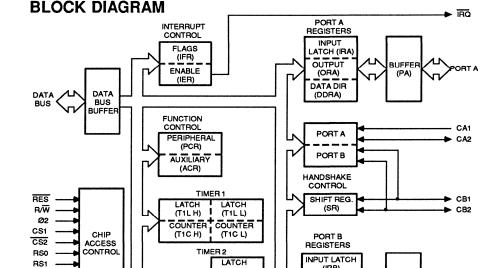

#### DESCRIPTION

The VL6522/VL65C22 are flexible I/O devices for use with the 65XX family of processors. The VL65C22 is a CMOS implementation of the VL6522 device. Both include functions for programmed control of up to two peripheral devices (ports A and B). Two programcontrolled 8-bit bidirectional peripheral I/O ports allow direct interfacing between the microprocessor and selected peripheral devices. Two programmable Data Direction Registers (A and B) allow selection of data direction (input versus output) on an

individual line-by-line basis. Also provided are two programmable 16-bit counter/timers with latches. Timer 1 may be operated in a one-shot interrupt mode with interrupts on each count-tozero, or in a free-running mode with a series of evenly spaced interrupts. Timer 2 functions both as an interval and pulse counter. Serial data transfers are provided by a shift register. Application versatility is further increased by various control registers, including an interrupt flag register, an interrupt enable register, and two function control registers.

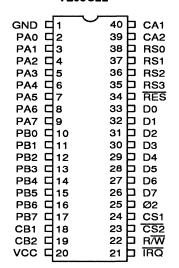

#### PIN DIAGRAM

#### VL6522 **VL65C22**

(T2L L)

COUNTER

(T2C L)

(T2C H)

(IRB)

BUFFE

OUTPUT

(ORB)

DATA DIR (DDRB)

#### ORDER INFORMATION

RS2

RS<sub>3</sub>

| Part                                                       | Techn-                       | Clock     | Package                                                                                       |

|------------------------------------------------------------|------------------------------|-----------|-----------------------------------------------------------------------------------------------|

| Number                                                     | ology                        | Frequency |                                                                                               |

| VL6522-01PC<br>VL65C22-01PC<br>VL6522-01QC<br>VL65C22-01QC | HMOS<br>CMOS<br>HMOS<br>CMOS | 1 MHz     | Plastic DIP Plastic DIP Plastic Leaded Chip Carrier (PLCC) Plastic Leaded Chip Carrier (PLCC) |

| VL6522-02PC<br>VL65C22-02PC<br>VL6522-02QC<br>VL65C22-02QC | HMOS<br>CMOS<br>HMOS<br>CMOS | 2 MHz     | Plastic DIP Plastic DIP Plastic Leaded Chip Carrier (PLCC) Plastic Leaded Chip Carrier (PLCC) |

| VL65C22-03PC                                               | CMOS                         | 3 MHz     | Plastic DIP                                                                                   |

| VL65C22-03QC                                               | CMOS                         |           | Plastic Leaded Chip Carrier (PLCC)                                                            |

| VL65C22-04PC                                               | CMOS                         | 4 MHz     | Plastic DIP                                                                                   |

| VL65C22-04QC                                               | CMOS                         |           | Plastic Leaded Chip Carrier (PLCC)                                                            |

# DOUBLE-DENSITY FLOPPY DISK CONTROLLER (DDFDC)

#### **FEATURES**

- · Address mark detection circuitry

- Software control of

- -Track stepping rate

- -Head load time

- —Head unload time

- · IBM compatible in both single- and double-density format

- Programmable data record lengths: 128, 256, 512, 1024, 2048, 4096 or 8192 bytes/sector

- Multi-sector and multi-track transfer capability

- · Controls up to four floppy disk drives

- Data scan capability—will scan a single sector or an entire track of data fields, comparing on a byte-by-byte basis data in the processor's memory with data read from the disk

- · Data transfers in DMA or non-DMA mode

- · Parallel seek operations on up to four drives

- Directly compatible with an 8-bit or 16-bit synchronous microprocessor bus including Z-80/8080A/8085A, 8086, and 8088

- Replaces the NEC μPD765A, Intel 8272A, and Rockwell 6765A

- Single phase 4 or 8 MHz clock

- Single +5 volt power supply

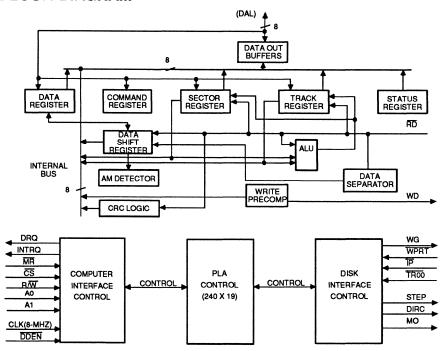

#### **DESCRIPTION**

The VL6765 Double-Density Floppy Disk Controller (DDFDC) interfaces up to four floppy disk drives to an 8-bit or 16-bit microprocessor-based system including Z80, 8080A, 8085A, 8086, and 8088. The DDFDC simplifies the system design by minimizing both the number of external hardware components and software steps needed to implement the floppy disk drive (FDD) interface. Control signals supplied by the DDFDC reduce the number of components required in external phase locked loop and write precompensation circuitry. Memory-mapped registers containing commands, status and data simplify the software interface. Built-in functions reduce the software overhead needed to control the FDD interface. The DDFDC supports both the IBM 3740 Single-Density (FM) and IBM System 34 Double-Density (MFM) formats.

The DDFDC interfaces directly to the synchronous microprocessor bus and operates with 8-bit byte length data transferred on the bus in either DMA or non-DMA mode. In DMA mode, the CPU need only load the command into the DDFDC and all data transfers occur under DMA control. The VL6765 is directly compatible with the Z8410/µPD8257 Direct Memory Access Controller (DMAC). In non-DMA mode, the DDFDC generates an interrupt to the CPU indicating that a byte of data is available.

Controller commands, command or device status, and data are transferred between the DDFDC and the CPU via six internal registers. The Main Status Register (MSR) stores the DDFDC status information while four additional status registers provide result information to the CPU following each controller command. The Data Register (DR) stores actual disk data, parameters, controller commands and FDD status information for use by the CPU.

#### **PIN DIAGRAM**

#### ORDER INFORMATION

| Part<br>Number                            | Clock<br>Frequency | Package                                                    |

|-------------------------------------------|--------------------|------------------------------------------------------------|

| VL6765-04PC<br>VL6765-04CC<br>VL6765-04QC | 4 MHz              | Plastic DIP Ceramic DIP Plastic Leaded Chip Carrier (PLCC) |

| VL6765-08PC<br>VL6765-08CC<br>VL6765-08QC | 8 MHz              | Plastic DIP Ceramic DIP Plastic Leaded Chip Carrier (PLCC) |

#### Note:

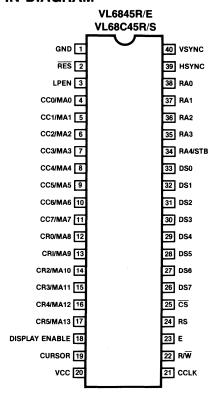

# VL6845 CRT CONTROLLER FAMILY AND VMC68C45 MEGACELL DESIGN KIT

#### **FEATURES**

- CRT Controller Family—

Rev E compatibility with SY6845E

Rev R compatibility with MC6845

CMOS versions available:

CMOS Rev R compatible with

MC6845R1, MC6845 and

MC146845 CMOS Rev S compatible

with HD6845S

- Internal refresh address generation

- Character clocks up to 5 MHz

- Bus clocks up to 3 MHz

#### **DESCRIPTION**

The VL6845X and VL68C45X are a family of CRT controllers that are widely used in both bit-mapped and character-mapped applications for both terminals and personal computers. The VL6845 family offers compatibility with the Motorola family of HMOS

controllers while the VL68C45 family allows designs to consume less power through the use of CMOS technology. In addition to compatibility with both the Motorola and Hitachi families, the VL68C45R also contains enhancements found in the MC6845R1. These enhancements allow for higher resolution displays without extra external hardware.

#### **PIN DIAGRAM**

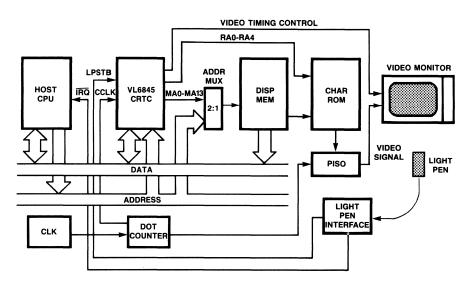

# SYSTEM DIAGRAM

#### **ORDER INFORMATION**

| Part<br>Number                                         | Clock | Frequency | Part<br>Number                                         | Clock | Frequency |                                                                                                         |

|--------------------------------------------------------|-------|-----------|--------------------------------------------------------|-------|-----------|---------------------------------------------------------------------------------------------------------|

|                                                        | Bus   | Character |                                                        | Bus   | Character | Package                                                                                                 |

| VL6845R-23<br>VL68C45R-23<br>VL68C45S-23               | 2 MHz | 3 MHz     | VL6845E-33<br>VL6845R-33<br>VL68C45R-33<br>VL68C45S-33 |       | 3 MHz     | To specify package type,                                                                                |

| VL6845E-24<br>VL6845R-24<br>VL68C45R-24<br>VL68C45S-24 |       | 4 MHz     | VL6845E-34<br>VL6845R-34<br>VL68C45R-34<br>VL68C45S-34 | 3 MHz | 4 MHz     | add the appropriate suffix to the part number:  PC = Plastic DIP  CC = Ceramic DIP  QC = Plastic Leaded |

|                                                        |       |           | VL6845R-35<br>VL68C45R-35<br>VL68C45S-35               |       | 5 MHz     | Chip Carrier (PLCC)                                                                                     |

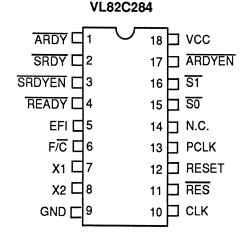

### **CMOS CLOCK GENERATOR AND INTERFACE**

#### **FEATURES**

- Generates clock for Intel 286-type microprocessor-based systems

- External TTL source or crystal may be used as frequency source.

- On-board crystal oscillator

- Provides READY signal for system synchronization

- · Generates system reset

- Schmitt trigger reset input assures stability and noise immunity

- Low power consuming CMOS technology

- · Single 5 V power supply required

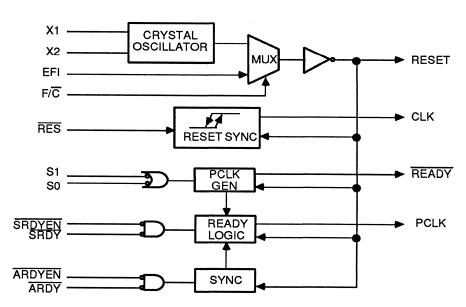

#### DESCRIPTION

The VL82C284 is a clock generator and driver that provides clock and interface signals to Intel 286-type microprocessor-based systems. All device output signals are synchronized to the output clock signal.

The clock input and output frequencies are twice the frequency used internally by the microprocessor in the system. To avoid confusion, the clock frequency in the order information represents the internal system microprocessor clock frequency (e.g., the devices listed as 8

MHz would actually have an input crystal or a TTL signal frequency of 16 MHz).

The VL82C284 also supplies the system with a high-noise-immunity reset, as well as a synchronous peripheral clock and a synchronous READY to indicate the completion of the current bus cycle.

The peripheral clock is controlled by two status input signals, which may be left open if not used.

The VL82C284 is available in an 18-pin ceramic and plastic DIP, as well as in a plastic leaded chip carrier.

#### **PIN DIAGRAM**

#### **BLOCK DIAGRAM**

#### ORDER INFORMATION

| Part<br>Number                                  | Clock<br>Frequency | Package                                                    |

|-------------------------------------------------|--------------------|------------------------------------------------------------|

| VL82C284-06PC<br>VL82C284-06QC<br>VL82C284-06CC | 6 MHz              | Plastic DIP Plastic Leaded Chip Carrier (PLCC) Ceramic DIP |

| VL82C284-08PC<br>VL82C284-08QC<br>VL82C284-08CC | 8 MHz              | Plastic DIP Plastic Leaded Chip Carrier (PLCC) Ceramic DIP |

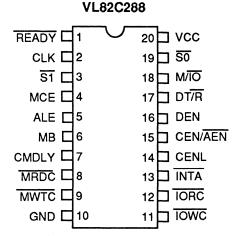

#### **CMOS BUS CONTROLLER**

#### **FEATURES**

- Both local and system bus commands and control are provided

- Supports both Multibus<sup>®</sup> and highspeed bus cycle operating modes

- · High-current output drivers

- Flexible command timing

- High degree of system configuration flexibility

- Low power consuming CMOS technology

- · Single 5 V power supply

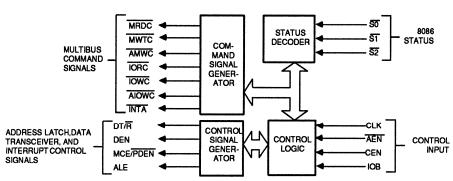

#### DESCRIPTION

The VL82C288 is a CMOS bus controller for use in Intel 286-type microprocessor-based systems. A mode select pin allows strapping the device for Multibus operation or for short bus cycles. The device also provides separate command outputs for memory and I/O devices. The data bus is controlled by separate data direction and data enable signals.

A system clock provides the timing control required by the microprocessor-based system. The device clock input is

twice the system clock speed. To avoid confusion, the clock frequency listed in the order information is the system clock frequency (e.g., the devices listed as 8 MHz Clock Frequency, would have an input clock of 16 MHz).

The VL82C288 meets the timing and drive requirements to satisfy the IEEE-796 standard for Multibus.

The VL82C288 is available in a 20-pin ceramic or plastic DIP, as well as in a plastic leaded chip carrier.

#### **PIN DIAGRAM**

#### **BLOCK DIAGRAM**

#### ORDER INFORMATION

| Part<br>Number                                  | Clock<br>Frequency | Package                                                    |

|-------------------------------------------------|--------------------|------------------------------------------------------------|

| VL82C288-06PC<br>VL82C288-06QC<br>VL82C288-06CC | 6 MHz              | Plastic DIP Plastic Leaded Chip Carrier (PLCC) Ceramic DIP |

| VL82C288-08PC<br>VL82C288-08QC<br>VL82C288-08CC | 8 MHz              | Plastic DIP Plastic Leaded Chip Carrier (PLCC) Ceramic DIP |

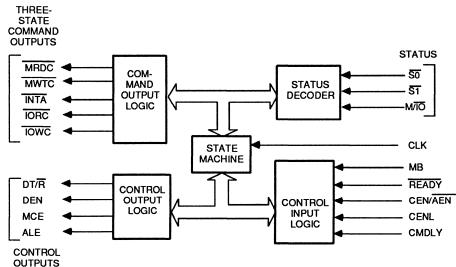

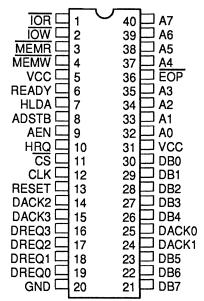

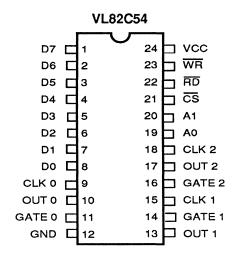

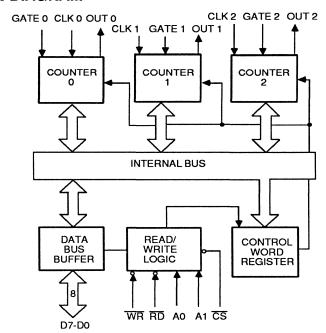

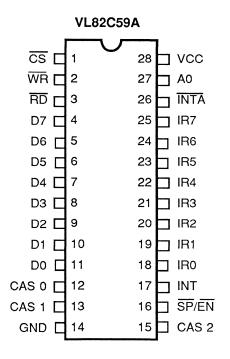

## **CMOS DIRECT MEMORY ACCESS (DMA) CONTROLLER**

#### **FEATURES**

- Low-power CMOS version of popular 8237A DMA controller

- Four DMA channels

- Individual enable/disable control of DMA requests

- Directly expandable to any number of channels

- Independent auto-initialize feature for all channels

- High performance 8 MHz version available

- Transfers may be terminated by endof-process input

- Software-controlled DMA requests

- Independent polarity control for DREQ and DACK signals

#### DESCRIPTION

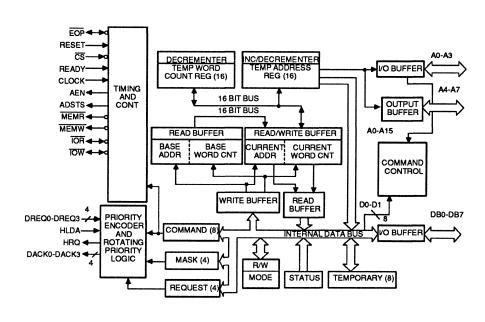

The VL82C37A Direct Memory Access (DMA) Controller serves as a peripheral interface circuit for microprocessor systems, and is designed to improve system performance by allowing external devices to directly transfer information from the system memory. Memory-to-memory transfer capability is also provided. The VL82C37A DMA Controller offers many programmable control features that enhance data throughput and system performance. Dynamic reconfiguration is permitted under program control.

The VL82C37A is designed to be used with an external 8-bit address register

such as the 8282. In addition to the four independent channels, the VL82C37A is expandable to any number of channels by cascading additional controller devices.

Three basic transfer modes allow the user to program the types of DMA service. Each channel can be individually programmed to auto-initialize to its original condition following an end-of-process (EOP) input. Each channel also has a 64K address and word count handling ability.

The VL82C37A DMA Controller is available in 5 MHz and 8 MHz clock frequencies.

#### **PIN DIAGRAM**

#### VL82C37A

#### **BLOCK DIAGRAM**

#### ORDER INFORMATION

| Part<br>Number | Clock     | Doolsono                           |

|----------------|-----------|------------------------------------|

| Number         | Frequency | Package                            |

| VL82C37A-05PC  | ,         | Plastic DIP                        |

| VL82C37A-05CC  | 5 MHz     | Ceramic DIP                        |

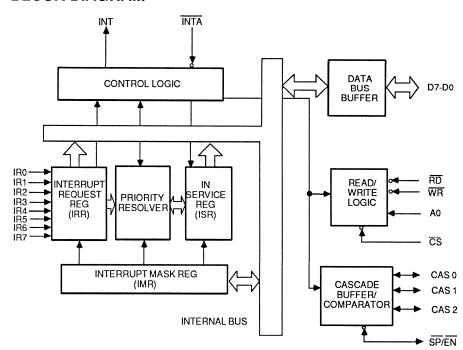

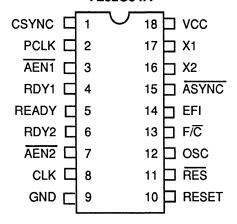

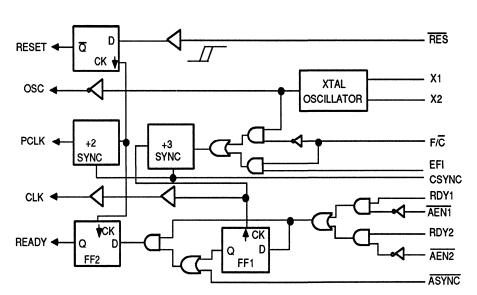

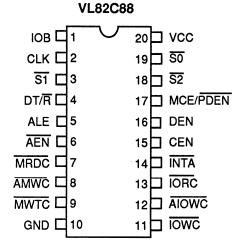

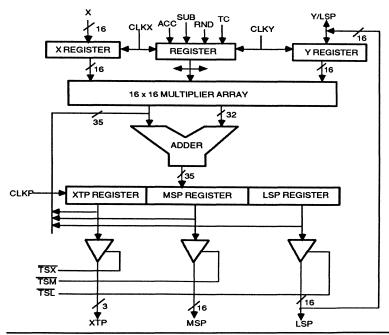

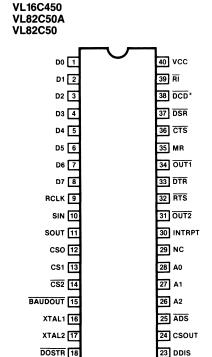

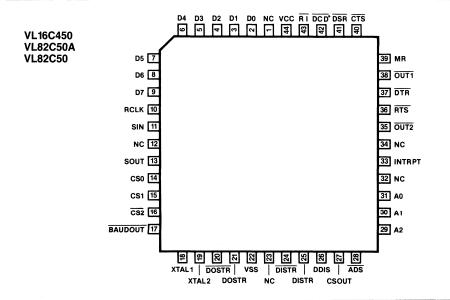

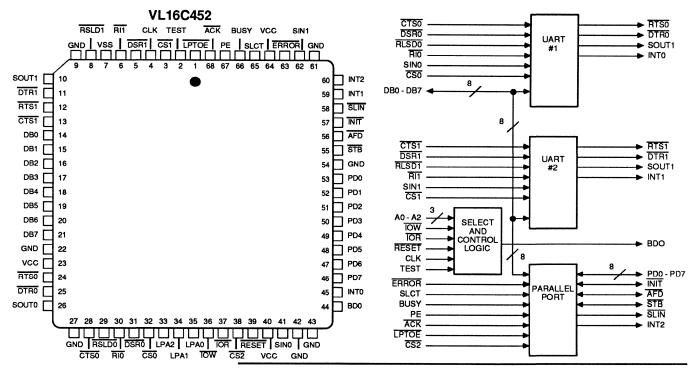

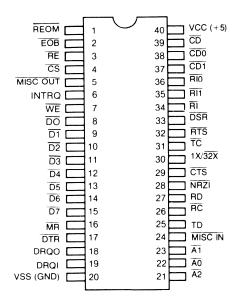

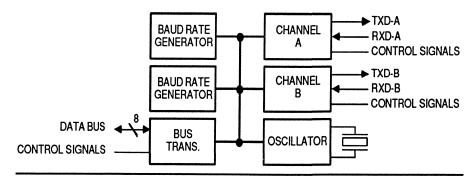

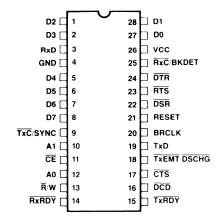

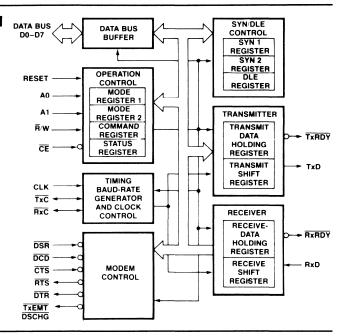

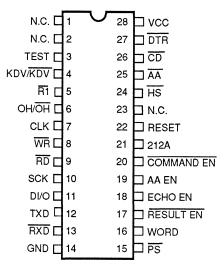

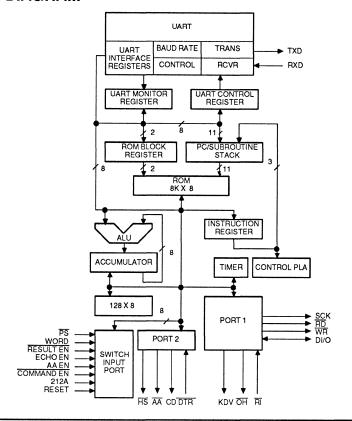

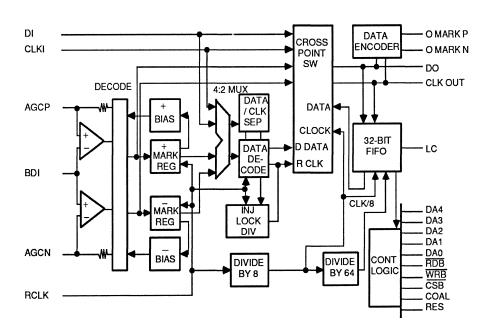

| VL82C37A-05QC  |           | Plastic Leaded Chip Carrier (PLCC) |